By Chris Browy, VP Sales and Marketing at Avery Design Systems

The evolution of NVMe® technology has been spectacular, starting with the basic PCIe-based SSDs and expanding to all-flash disaggregated, composable storage systems that involve an alphabet soup of standards. NVMe technology now embodies a set of standards, and system architects must be able to assess how systems and software best utilize these transport layers to communicate with non-volatile memory using other industry standard transport protocols like PCI Express, RDMA, and TCP.

Like all standards, the NVMe standard continues to evolve to meet new and changing requirements. It needs to continue to scale with each new generation of SSDs to ensure that performance and low latency needs are met for a variety of applications –- from mobile devices, laptops, desktops to servers in the cloud data center. That’s why the NVM Express group is so important. The non-profit organization provides a platform for the necessary cooperation, compliance and definition of the NVMe standards as the industry evolves. In its own words, the organization “is designed from the ground up to deliver high bandwidth and low latency storage access for current and future NVM technologies.”

The key here if you’re a product developer is future proofing. With each incremental incarnation of the standard, new features get added, so, engineers involved in designing, verifying and validating SSD systems need to keep updated. In the most recent update, the NVMe 2.0 specifications were restructured to enable faster and simpler development of NVMe solutions, and to support the increasingly diverse NVMe device environment.

Of course, when new specifications are made available, product developers want to be sure they are 1) taking full advantage of the latest features, and 2) are complaint with the standard. In the form of early design testing and verification, training, education and hands-on use are all critical. And with this being the ultra-competitive electronics industry, development time is of the essence.

Instead of waiting to attend plug fests to run compliance tests at the end of a NVM project, there’s a way to run compliance testing while a project is still in the design phase, using emulation, when it’s much easier to make changes. Doing conformance checking early in the design process not only saves time, but also eliminates surprises that occur when waiting until production, when it’s too late to make design changes. This is a great example of Shift-left thinking – to move testing much earlier during the product lifecycle.

No one knows more about compliance testing than the folks at the University of New Hampshire InterOperability Lab (UNH-IOL). It is an independent lab that tests networking and data communications products. Since 1988, the laboratory has fostered multi-vendor interoperability and has grown steadily into one of the industry’s premier independent proving grounds for new technologies. The folks at UNH-IOL pride themselves on their neutrality and openness, saying “We exist because of the need for an independent, neutral, third party that can serve as arbiter for the networking industry. We maintain an unmitigated commitment to the confidentiality and security of customer information provided in an unbiased safe haven, enabling industry members to resolve issues collaboratively.”

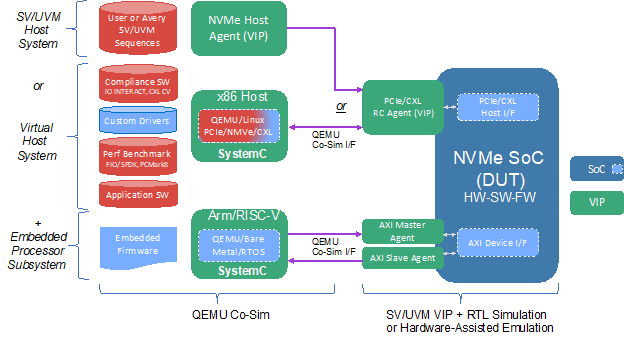

This is why Avery Design Systems was happy to work with the UNH-IOL on developing a workshop to help engineers understand what’s new in the latest NVMe standard, and, more importantly, how to pre-validate designs that leverage the standard. In the session, we describe how engineers can perform faster testing and validation using IOL INTERACT™, a software platform that expedites and automates the testing of NVMe SSDs and NVMe-oF™ products. When combined with a commercial system-level verification platform, like Avery’s QEMU-NVMe system as one use case, developers can perform full system, pre-silicon simulation to ensure the proper performance of designs that include NVMe technology.

In the workshop, we showed how by co-simulating the SoC RTL code with the QEMU open software virtual machine, a software engineer can then develop and build their firmware, drivers and even applications to run on a Linux or Windows platform. Issues with software can be debugged with GDB or KGDB, while using the cycle accurate SystemVerilog RTL for the SoC.

The complete workshop is available for viewing here.